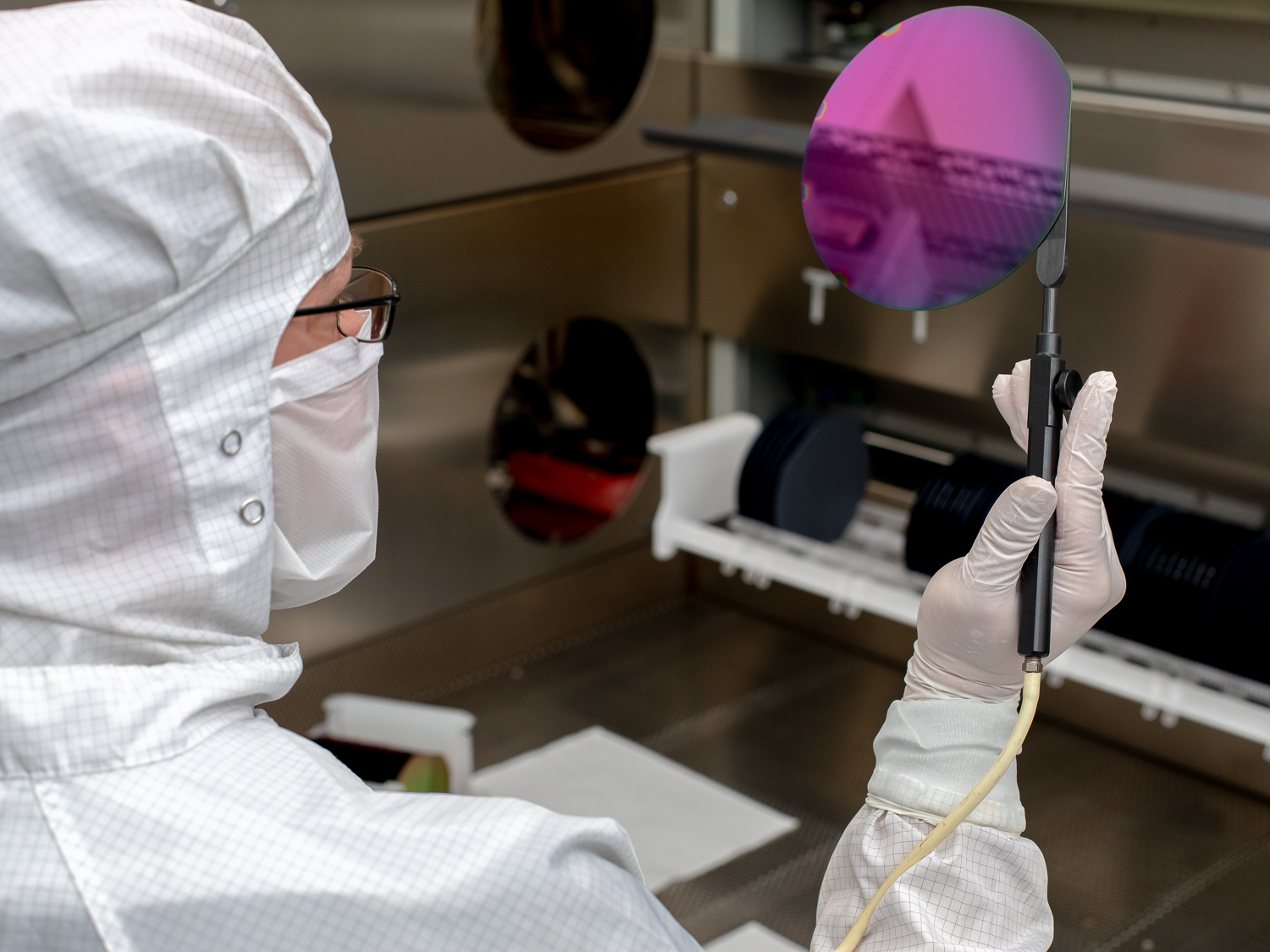

Thermische Oxidation von Silizium

CMOS-kompatible Quarzofenprozesse (Centrotherm), Trocken- und Nassoxidation 100 und 150 mm Wafergröße, Chargenmenge: bis zu 50 Wafer pro Run.

- LOCOS-Oxid (LPCVD-Nitridmaskenschicht)

- Gateoxid, Standarddicke 40 nm

- Feldoxid, Standarddicke 1000 nm

- Kundenspezifische Oxidschichten werden angeboten, Dickenbereich 10 nm bis 1500 nm

Homogenität (Dicke) über den Wafer: <2% durchschnittliche Homogenität (Dicke) von Wafer zu Wafer: <3% durchschnittliche Homogenität (Dicke) von Charge zu Charge: <5%